| スレッド表示 | 新しいものから | 前のトピック | 次のトピック | 下へ |

| 投稿者 | スレッド |

|---|---|

| webadm | 投稿日時: 2006-12-4 22:58 |

Webmaster   登録日: 2004-11-7 居住地: 投稿: 3086 |

Post-fitシミュレーションではpull-up抵抗が問題 後半のホストからのリードサイクルがおかしい原因はstart conditionのテストベンチパターンがsdaをHi-Zからlowにしているのが原因。

最初のライトサイクルはHi-Zから一旦Highにしてそれからlowにしているので問題無い。 本来は外部にpull-up抵抗があるのでHi-Zからlowにして正しいのだが、Post-fitシミュレーション時にはPULL-UP抵抗の記述が無視されてしまうのでうまくいかない。Behavioralシミュレーションでは有効なので問題無い。 ということはテストベンチを修正すればなんとかなるかも。 |

| webadm | 投稿日時: 2006-12-4 23:19 |

Webmaster   登録日: 2004-11-7 居住地: 投稿: 3086 |

3stateバスはPost-fitシミュレーションが面倒 あまり使いたくない3stateバス。I2Cはそれだから困る。

Post-fitシミュレーションではタイミングバイオレーションこそ出ないのでBehaviorシミュレーション通りに動くはずだが不安は残る。 テストベンチを変更してstart conditionの際にはHightからLowへsdaが遷移するように変更するとアドレス照合サイクルは正しく動作している。後続するデータ出力サイクルはこれまたsdaがHi-z状態になるので(バス上はpull up抵抗によってHighになるはず)それが入力としてフィードバックされるとsdaで駆動する内部信号が全滅となる。なんてこった。 |

| webadm | 投稿日時: 2006-12-6 9:36 |

Webmaster   登録日: 2004-11-7 居住地: 投稿: 3086 |

AlteraのI2Cリファレンスデザイン AlteraもI2Cリファレンスデザインを提供している。

こちらは68Kのようなホストバスインターフェースを備えたMaster/Slave両用IP coreという本格的なもの。 しかもテストベンチとしてMasterとSlaveを対向接続したものがついている。小規模でありながら売り物のIP Coreとなんら変わらないパッケージングである。小規模すぎるので売り物にならないということでリファレンスデザインとして公開されたのかもしれない。もちろん使用条件としてAltera社以外のデバイスには使わないことというのがあるのは当然。 AlteraのI2C IP coreは完全な単一クロックによる同期設計で、Xilinxの複数クロックの非同期設計とは大違い。 XilinxのはもともとI2Cのような劣悪なシリアルバス信号をそのままクロック信号として使うというあり得ない設計ではあるが、スレーブ専用にして単純化してあるので理解しやすいことはある。 AliteraのはMaster/Slave両モード兼用なのと単一クロック設計なので規模は大きい。Slaveだけに縮小したいと言っても簡単に直せるものではないと思う。それでもリソースはそれほど食わない。MAX-IIのようなCPLDにも収まる。もちろんそれ以外のロジックを追加する余地は無いけど。 Aletraのは汎用MPUインターフェースなのでシミュレーションするにもMPUのバスサイクルを生成するテストベンチが必須になる。それらは収録されているので利用することができる。 さてどうするか。 |

| webadm | 投稿日時: 2006-12-12 9:56 |

Webmaster   登録日: 2004-11-7 居住地: 投稿: 3086 |

Xilinxにも同じのがあった 出所は同じと思われるまったく同じリファレンスデザインがXilinxからも提供されていた。

uPインターフェースなMaster/Slave両用のcore。 でもとりあえずI2CでつながるRAMみたいなものを作るにはちょっと趣向が違う。uP無しでハードウェアだけで買ってに動いてくれるのを作りたいのだけれども。 やはり自分で仕様決めてデザインした方が早いかも。 |

| webadm | 投稿日時: 2006-12-29 21:13 |

Webmaster   登録日: 2004-11-7 居住地: 投稿: 3086 |

エレツール株式会社のFreeIP 改めて探してみたらエレツール株式会社さんのところで昔から同期式のI2CスレーブデバイスのデザインがFreeIPとして公開されてました。

作りたかったものと寸分違わないのでそのまま使わせて頂くことに。同期型設計なのでかなり綺麗な作りである。 Quratus IIでコンパイルしたらスレーブアドレスの比較のところで7ビットのスレーブアドレスと9ビットのシフトレジスタを比較しているところがあって警告が出た。比較したいところはシフトレジスタの上位7ビット(最初に送られてくる7ビット)なのでそのように修正。そのままにすると常に一致しない論理が生成されてしまうらしい。 まだシミュレーションはこれから。 (2010/4/11) 検索でi2cスレーブのfreeipを探しにこちらへやってくる方が結構多いので確認したらここで使用したi2cスレーブの優れた実装コードをずっとFPGAインフォメーションさんからダウンロードしたものと記憶違いをしていたことが判明。FPGAインフォメーションさんのところはi2cスレーブのipコアは有償でしか提供されていないので改めて探したところ、エレツール株式会社さんのWebページで今もFreeIPとして公開されているものを利用したことがソースコードを見比べて確認した次第。タイトルや本文を訂正しました。こちらへ検索サイト経由で来られた方には大変申し訳ありませんでした。 |

| webadm | 投稿日時: 2006-12-30 5:22 |

Webmaster   登録日: 2004-11-7 居住地: 投稿: 3086 |

シミュレーション結果も良好 単相クロック同期なので十分なクロック数分入力信号がサンプルされるようにテストベンチを作成すれば問題なく期待通り動いてくれた。

使い慣れたQuartus IIでやったのだがISEでも問題なくできると思われる。 AlteraやXilinxから提供されているMPU I/Fを前提としたリファレンスデザインよりもかなり扱い易い。これに好きなステートマシンとかを追加すれば好みの機能をもったI2Cスレーブデバイスが作れる。 すばらしい。 |

| webadm | 投稿日時: 2006-12-30 18:02 |

Webmaster   登録日: 2004-11-7 居住地: 投稿: 3086 |

実際にCPLDで動いた さっそくXILINXのCPLDデザインキット基板用にISEでコンパイルしてみた。

XC2C256だとSpeed優先では余裕がないということでArea優先にしたら余裕で入った。 シミュレーションしようとしたらうっかりしてシミュレーターをISEシミュレーターのままでプロジェクトを作ってしまい、にっちもさっちもいかず。ISEシミュレーターは珍しくコンパイル型のシミュレーターなのでネットリストをC/C++コードに変換されて実行される。しかしその変換がバグっていて多くの場合シミュレーションすらできない場合が多い。 諦めてそのまま動かしてみることにした。すんなり動いた。これでまだ手に入らない新しいI2Cインターフェースのデバイスを使ったマイコンのデバッグが可能になる。 結果はAlteraのQuartus IIのシミュレーターで出てきた結果と寸分違わぬ波形が出てきた。ACKの前に微妙にヒゲが出てしまうところまでシミュレーターは忠実に再現していたことになる。これはSCLがLowの区間なのでSDAが変化して良いので問題ない。 とりあえずPICのI2Cで1Mbpsでつないでみて問題ないようだ(あらかじめCPLD基板についているクロックは1.843224MHzと低速なので手持ちの24MHzのものに交換してある)。 |

| webadm | 投稿日時: 2006-12-31 4:16 |

Webmaster   登録日: 2004-11-7 居住地: 投稿: 3086 |

トラ技付録MAX II(EPM240T100C5)にも入った 最初FLEX10K10でコンパイルした時はLE数が305と大きくLE数がそれより少ないトラ技付録MAX II基板(EPM240T100C5)には入らないだろうと諦めていたが、やってみると所要LE数がFLEX10Kよりも少ない209という結果になって余裕で入った。

MAX IIの中身はコンフィグレーション用FLASHとALETRAのFPGAが一緒に内臓されたような感じだが、FPGA部分は古いFLEXシリーズのものよりも使用効率が良いようである。 これなら大きいXILINXのCPLDデザインキット基板よりも小さくて良い気がする。 |

| webadm | 投稿日時: 2006-12-31 6:10 |

Webmaster   登録日: 2004-11-7 居住地: 投稿: 3086 |

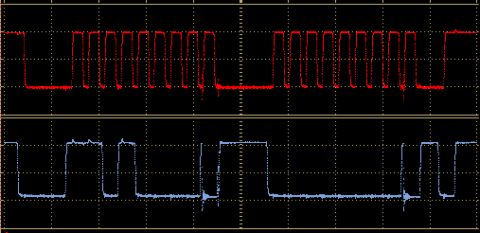

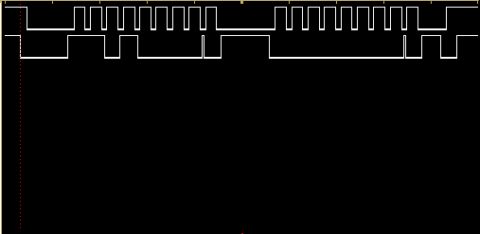

持ち腐れ気味のHP16500Bで波形観測 もてあまし気味のHP16500Bのオシロとロジアナで波形を見てみた。

ちょっとトリガーの設定がオシロはやりづらいやっと単発トリガーがかかるようになって取れたのが以下の波形。シミュレーションパターンと同じもの。Quartus IIのシミュレーション結果もこれとまったく同じだった。  同じ波形をロジアナでキャプチャしたもの。ヒゲの部分はちょうどSCLがlowの期間に収まっている。  実際に1Mbpsでちゃんと動いているかはやはりオシロやロジアナを使って観測しないといけない特にマスター側がPICとかソフトで制御している場合。動いているけど100Kとか400kとか低速で動かしていたりすると目もあてられない。 |

| webadm | 投稿日時: 2007-1-2 19:43 |

Webmaster   登録日: 2004-11-7 居住地: 投稿: 3086 |

ようやく完成 とりあえず仕事のデバッグ用に使うI2CデバイスエミュレーターがCPLDを使って完成した。

A/Dコンバーターとかの機能をエミュレートするために簡単な乱数生成機と割り込み信号をエミュレートするロジックを追加。それといろいろな内部レジスタをエミュレートさせたり。 これでPIC側のファームウエアからは本物と見分けがつかない。ハードウェアだけでシステムを作る場合にはシミュレーションモデルとして利用価値があるかもしれない。欲しいという話は聞かない、Behavioralシミュレーションだけだったらテストベンチを書けばなんとかなる範囲ではあるが。 やはりじっくり腰を落ち着けてじっくり設計を検討したわけではなく出来るところから書いてシミュレーションで結果を見るというなんともアジャイルメソッド的なやり方だったのはいただけない。デバッグ用とはいえ、ちゃんと本物に忠実な振る舞いをしないといけないのでそれなりにテストしないといけない。 今回はまったのはQuartus IIでのMAX IIへのプログラミング時に稼働中のままプログラミングすると現在動作しているデザインにはまったく影響が無いという点。MITOUJTAGトラ技評価版に慣れていたので知らなかった。 暇があればVerilogでも書いてみよう。 それにしてもMAX IIやCoolrunner IIで最大動作クロック周波数が100MHzを楽に超えているというのはすごい。エレツール株式会社さんのI2C I/F FreeIPは良く出来ている。バグは残してあるみたいだけど。 (2010/4/11) i2c FreeIPの公開元が間違っていましたので正しくエレツール株式会社さんと訂正させて頂きました。 |

| « 1 (2) 3 » | |

| スレッド表示 | 新しいものから | 前のトピック | 次のトピック | トップ |

| 投稿するにはまず登録を | |