| フラット表示 | 前のトピック | 次のトピック |

| 投稿者 | スレッド |

|---|---|

| webadm | 投稿日時: 2006-7-22 19:58 |

Webmaster   登録日: 2004-11-7 居住地: 投稿: 3086 |

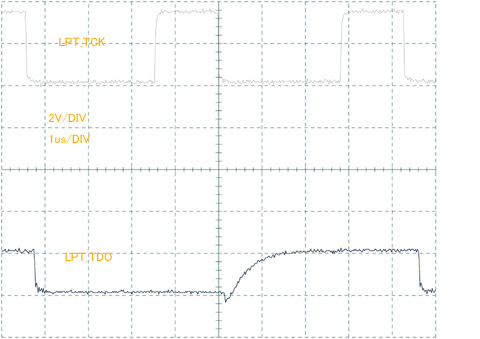

TCK-TDOターンアラウンドタイム 気になるので実際に拙作プログラミングケーブルのプリンターポートからのTCK入力立ち下がりからプリンターポートへのTDO立ち上がりのターンアラウンドタイムを観測してみた。

入力側のバッファはエミッタ接地が2段なのでとてつもなく立ち上がりがなまっている。立ち下がりはどうでもいいのにシャープすぎるというアンバランスなのを思い出した。 1.8V動作のMAX IIで観測したものだが、LPT_TDOのレベルがやっとTTL閾値の2.1v付近に達するのにだいぶ時間がかかることが分かる。次のTCKの立ち上がりの頃には十分安定しているが、それ以前にサンプルされると誤りが生じる可能性が十分ある。 これを改善するには、 (1)立ち上がり特性を良くする (2)出力レベルを上げる のどちらかもしくは両方が必要。 2.5v動作では(2)が改善されるのでMITOUJTAGも問題なく動作するのでどちらかというと出力レベルをもっと上に引っ張り上げるのがよさそうである。しかしそれはそれで難しいところ。 |

| フラット表示 | 前のトピック | 次のトピック |

| 投稿するにはまず登録を | |