| フラット表示 | 前のトピック | 次のトピック |

| 投稿者 | スレッド |

|---|---|

| webadm | 投稿日時: 2006-4-30 12:14 |

Webmaster   登録日: 2004-11-7 居住地: 投稿: 3084 |

PoorMan's Byteblaster II お待ちかねトランジスタだけでできたALTERA BYTEBLASTER IIもどきプログラミングケーブルを製作してみた結果報告。

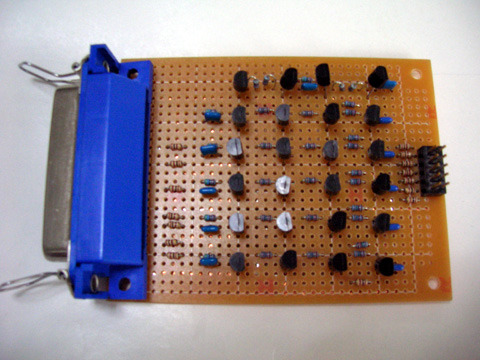

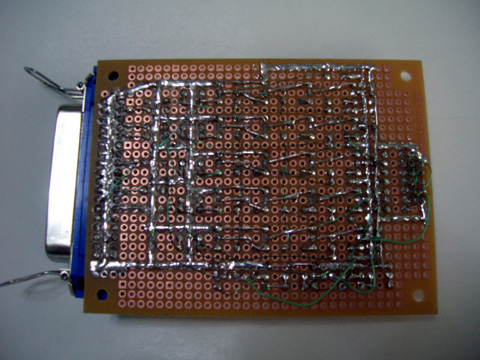

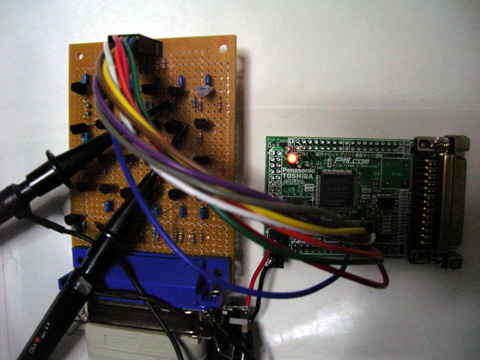

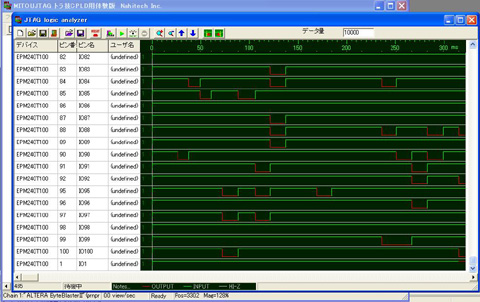

整然と24石のトランジスタ(後でもう1個増え25石)が並んでいる姿は美しいというか本当に作ってしまったのはアホというか。裏の配線はこんな感じ。  同じ回路パターンなので配線やハンダ付けがつらいかなと想像していたら予想に反して、単調な繰り返しが毛糸編みに似ていて予想外に安堵感があり、人類共通の工芸の遺伝子が発動しているのを実感。意外に長い時間続けても疲れないのが不思議。かえって繰り返し性の無い部分が短時間でも疲れがたまる。 実は見かけは綺麗で動作しそうに見えて大きな落とし穴があった。 実際に動作確認のためにコンフィグレーションできるFPGA/CPLDボードボードが必要。こないだトラ技に付録についてきたCPLD基板を使うために高いけど一緒に部品セットも購入してあったのでそれも組み上げておいた。こちらはハンダ付けする部品は少ないがべたグランドプレーンがあるのでグランド部分は温度が上がりにくく慣れないとハンダ付けは難しい。おまけに部品セットに入っていたJTAG用の10pinコネクタがメスだったり。仕方がないので手持ちのピンヘッダを切って挿すことに。メスのコネクタは電源ソケットとして活用。 JTAGピンの接続ケーブルは端子金具を圧着するのが慣れるまでが大変で、圧着器具はあるもののどの穴でかしめればいいのか分かるまで何本か出来の悪いのを作るはめになった。AWG20では少し配線材としては太いということも判明。ちょっと剛性が高すぎてしなやかさに欠ける。もう少し細めのがよさそうだ。それと浅草ギ研のは金具が金属リールについたままの状態なので引きちぎって使うタイプ。かしめた後裸の状態ならピンヘッダにしっかり刺さるものの、ハウジングにいれるとスカスカな時があり、どうもハウジング内の金具位置の遊びが大きめなのでしっかり奥まで金具を入れないと届かないようだ。 そんなこんなでやっとCPLD基板と拙作プログラミングケーブルをつなぐことができた。しかしここで問題発生。接続してCPLD基板に電源を入れると時々異常に大きな電流が流れてレギュレーターがオーバーヒートしてしまう。良く調べてみると最初にこしらえたグランド信号のケーブルが少し心線がばらけてしまっていて隣のVccピンにハウジング内で短絡を起こしていたことが判明。とりあえずグランドはもう一本あるので出来の悪い方は引っこ抜いてしまうことで解決。 ようやくQuartus IIでトラ技付録のLED点灯のやつをやってみることに。しかし最初のAuto Detectを試してみると、なにもつないでない状態で行うのとは少し時間が長いもののデバイスを検知できないという結果。長い時間の間はJTAGのTCKがずっとトグルしているのがオシロで観測された。周期は2usで周波数にすれば0.5MHzと基本的には余裕なはず。 更にオシロでTCKの出力波形を観測すると慟哭の事実を眼にすることに。まず波形がつぶれていてHighレベルが閾値ぎりぎり。ロジックチェッカではパルスが確認できるが、デューティ比も悪い。 どうもOutput Enableの制御に使っているPCのプリンタポートのデータラインのfan outが多すぎてレベルが下がってしまっているためか初段のトランジスタがまたしても機能していない。そのためTCKについて言えばトーテムポールの下側のトランジスタが常にOFF状態のままとなり辛うじてCPLD基板側でTCKがpull downしてあるので上側のトランジスタがエミッタフォロワー回路となり少しだけ出力波形が出ている感じ。 とりあえずOutput Enable信号を追加のトランジスタでエミッタフォロワーバッファを介して全バッファのOutput Enable入力として分配するように変更。これによってAuto DetectでEPM240とかが出てくるようになるが、プログラミングしようとするとverifyでエラーが出る。 どうもまったく前段のトランジスタがON/OFFしないのは変わらない。多少出力波形がメリハリがついてきたので少しまともになった程度らしい。 更にオシロであちこち観測点を変えながら繰り返しプログラミングを試してみると、あるところにプローブをあてた状態だと問題なくverifyが通り、LEDが点灯することを確認。ちゃんと動くじゃないか。  これが昔からある魔法のプローブ現象、つなげておくと動くけど外すとまた動かなくなる謎。上側のON/OFFしているトランジスタのベースにプローブをつなげた状態だとぎりぎり動く感じ。CFM(Configuration Flash Memory)のEraseやプログラムも問題ない、CFMに書き込んでやると電源を入れるとすぐにLEDが点灯する状態になる。CPLDとしてちゃんと使えるじゃないか。 ようやくトラ技付録のMITOUJTAG評価版を試してみる時がやってきた。とりあえずALTERAのケーブルとして接続設定をすると認識された。使い方がいまいち分からないのでロジアナ機能を試してみると、それらしい波形がサンプルできた。LED出力に使っているIO1ピンが見あたらないと思ったら一番下にあった。ちゃんと常時Hightが出力されている。  残念ながらMITOUJTAG評価版でCPLDをコンフィグレーションしてみるとWrite Failureとなってプログラミングできないようだ。Quartus IIの時と波形がちょっと違うのでタイミング的に厳しいのかもしれない。ロジアナ表示で使っていない他のIOピンはランダムに変化しているように見えるけど、あっているのだろうか? まあとりあえず原理動作は確認できたので、ブレッドボード上だとうまく動くのに実際に組むと違う動作をする問題を解決できれば上出来。試しに同じプリンターポートのTCK信号を以前こしらえたブレッドボード上の回路に入力してあたえてやるとこちらはちゃんと綺麗な出力がでる。違いと言えば出力負荷がブレッドボード上はテブナン終端で実機はpull downのみである点しかない。そこに原因があるのかもしれない。 うまく問題が解決できたら回路図を公開予定。 |

| フラット表示 | 前のトピック | 次のトピック |

| 投稿するにはまず登録を | |