| フラット表示 | 前のトピック | 次のトピック |

| 投稿者 | スレッド |

|---|---|

| webadm | 投稿日時: 2006-5-23 22:50 |

Webmaster   登録日: 2004-11-7 居住地: 投稿: 3087 |

純正ByteBlaster IIの新事実判明 出力イネーブル信号の互換性問題で、MAX+PLUS IIやQuartus IIそれにJam STAPL PlayerにMITOUJTAGトラ技評価版をとりまぜ純正ByteBlaster IIと拙作インチキケーブルの動作を比較検証してみると、Jam STAPL Playerでだけ拙作のケーブルが出力イネーブルにならない。

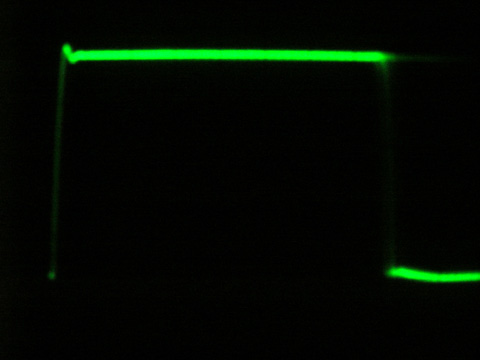

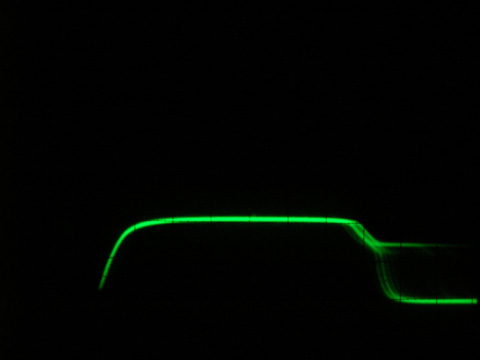

何故純正ByteBlaster IIはそれでも動くのか、Jam STAPL PlayerでJTAGのIDCODEスキャンをさせている間にプリンターポートの各信号ピンをロジックチェッカで確認してみたところ慟哭の新事実が判明。 純正ByteBlaster IIはPin6,7,9,14の他にPin36(手元のアンフェノール36ピンケーブルではここにnStrobe信号が結線されているようだ、Dsub-25だとPin1に該当)も出力イネーブル信号として使用していることが判明した。nStrobe信号はMITOUJTAGトラ技評価版では表示も制御もサポートされていないので確かめようが無かった。 さっそくスイッチングダイオードをつないでnStrobe信号でも出力イネーブルになるように変更するとJam STAPL Playerでもターゲットへ信号が出力されるようになった。 MAXIIでは問題ないが、自作のFLEX10KボードだとIRスキャンは問題ないがIDCODEが正常に読み出せない。他のツールではIRすらまともに読み出せない。違いというとJam STAPL Playerはインターブリタ動作のためTCKパルス間隔が他に比べて大変長いということぐらいしかない。TCKパルス幅はMITOUJTAGと同じで他に比べると短く1uSぐらいしかない。しかしトラ技MAXII CPLD基板ではどれも問題ない。この違いはやはりTCKの波形にあるのかもしれない。 そう思ってついに純正ByteBlaster IIをFLEX10Kボードにつないだ状態でFPGAのTCKピンにオシロをつないで波形を観測してみた。その結果、想像していたのとはまるで違っていた。  見事なまでのフルスイングである。写真で見えたのはバイポーラトランジスタではなくCMOS FETだったのだろうか。立ち上がりと立ち下がりどちらもシャープで文句のつけようが無い。これなら動いて当たり前である。FLEX10KボードのTCKラインには300pのセラコンを付けているがそれでも波形がなまったりしているわけではないのがすごい。 今度は拙作のインチキケーブルをつないで同じように観測してみると、同じスケールだが明らかにレベルが低く立ち下がりになにやらおかしな残像が見え隠れしている。立ち上がりエッジしか使わないPSモードは問題ないものの両エッジを使うJTAGでまともに動かない理由はこのあたりにありそうである。  よく見るとオーストラリア大陸にあるエアーズロックのようにも見えなくもない。 この波形が低い理由は分かっている。シミュレーションでもVCC側の2つのトランジスタのベースバイアス電圧が足らない(入力信号のレベルが低い場合)のでどちらかのトランジスタが完全にONにならないためである。オシロで観測すると出力イネーブル制御用のトランジスタは完全にONしているのでVceはほぼ0vに近いもののVCCにコレクタがつながっている方のトランジスタはL出力時には完全にOFFしているもののH出力時にVceが2.5vまでしか下がらない。これがレベルが頭打ちになる理由だ。シミュレーションだとどちらのトランジスタも完全にはONにならないため、出力は更にレベルが低く実用にならない状態になる。 なんとかVcc側のトランジスタを完全にONするようにできればかなり波形はまともになるのだが。 |

| フラット表示 | 前のトピック | 次のトピック |

| 投稿するにはまず登録を | |