| フラット表示 | 前のトピック | 次のトピック |

| 投稿者 | スレッド |

|---|---|

| webadm | 投稿日時: 2006-7-21 22:24 |

Webmaster   登録日: 2004-11-7 居住地: 投稿: 3087 |

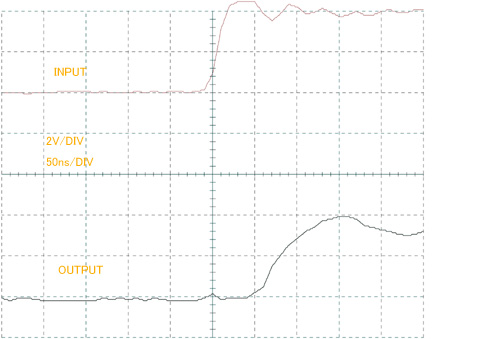

バッファ遅延時間の問題 あと拙作のプログラミングケーブルの現状の性能に問題があるのはバッファの遅延時間である。長いタイムスケールで見ると気にならない程度だが、拡大掃引すると立ち上がりの50%のところで入力から出力の遅延時間を計測すると50ns以上ある。更にJTAGではTDOがTCKの立ち下がりを受けて変化するので入力バッファでも同じような遅延があるとすると往復で遅延が100nsを超える。もしJTAGソフトウェアが十分短い遅延時間のプログラミングケーブルを前提にTCKの立ち下がりからTDOの遅延時間分しか待たないでTDOをサンプルしているとすれば拙作のプログラミングケーブルではセットアップ時間を満足しないのでサンプルデータに誤りが生じる。

たぶんMITOUJTAGはそんな感じなのかもしれない。Quartus IIとかは次のTCK立ち上がりのタイミングまでTDOサンプルを遅らしていると思われるので拙作のプログラミングケーブルでも問題なく動作する。 いずれにせよ遅延が大きすぎるのを直せば1.8v動作時のMITOUJTAGでの問題は無くなるのではないかと予想される。 もう少し高速なトランジスタを使えばいいのかも。今使っている2SC1815は遮断周波数が80MHzだが秋月とかにその10倍ぐらいのトランジスタが売っているのでそれを使えば少し応答性能が良くなるのかも。それかton/toff時間の短いFETを使う方が早いのかもしれない。 |

| フラット表示 | 前のトピック | 次のトピック |

| 投稿するにはまず登録を | |