| フラット表示 | 前のトピック | 次のトピック |

| 投稿者 | スレッド |

|---|---|

| webadm | 投稿日時: 2006-7-29 5:43 |

Webmaster   登録日: 2004-11-7 居住地: 投稿: 3086 |

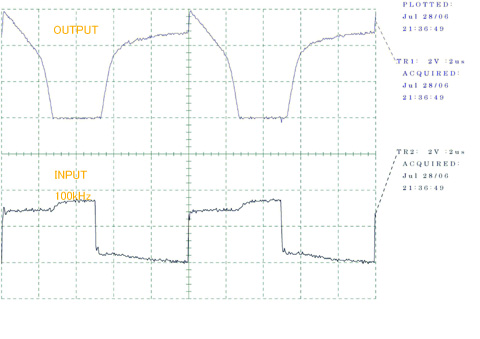

PチャネルMOSの場合 今度はFDS4675 PチャネルMOSを評価してみた。

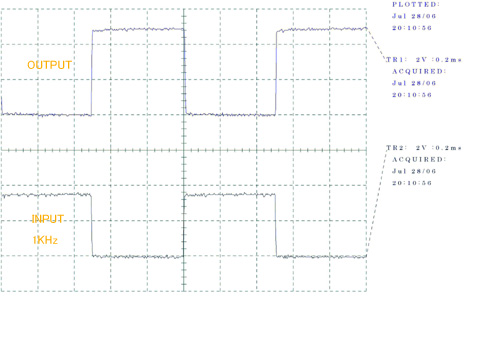

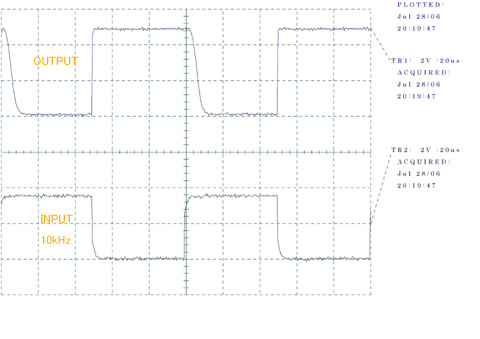

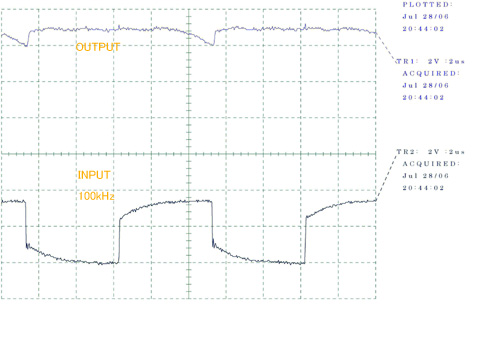

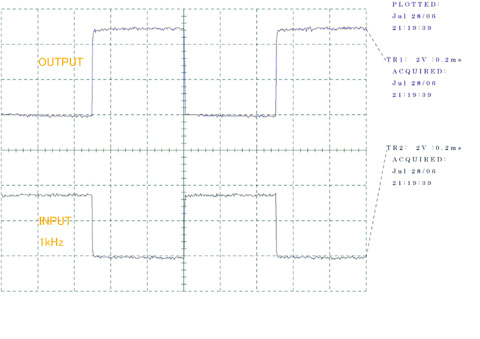

FDS4675はパッケージがSO-8(8pinフラットパッケージ)だがFETは1個しか入っていない。 リード線を継ぎ足してブレッドボード上でソース接地回路を組んで入力を与えたみた。まずは1kHzから。  この程度ならわずかしか遅れは目立たない。ON時(OUTPUTがL->H)は速いがOFF時は遅れが見える。入力レベルは5Vフルスイングではないがこれ以上レベルを下がってしまうとFETが完全にOFFしない(ゲートとソース間の電位差が2vを超えるとONし始めてしまう)。 入力周波数を上げていくと元々大きい遅延部分が目立ってくる(遅延時間そのものは変化しないがOFFが遅れるので次ぎのONまでの時間が周期が短くなるにつれ短縮してしまう)  どんどん周波数を上げると100kHzぐらいで遂にONしっぱなしの状態となってしまう。  NチャネルおよびPチャネルどちらも単独では高速なスイッチイングには向いていないことになる。 ならばNチャネルとPチャネルをトーテムポール接続したCMOSバッファを構成するしかない。シミュレーションではCMOS接続により違いの欠点(OFF時に大きな遅延が生じる)を他方が補う(ONが速い)ことによって立ち上がり立ち下がりとも高速にできる可能性がある。  これがCMOS回路での波形である。一見して立ち上がりも立ち下がりも遅延が無いように見える。しかし実際にはNチャネルMOSとPチャネルMOSが同時にONになっている期間があるため電流制限を入れないと貫通電流により両方のFETが高熱を発してしまう。周波数を上げると入力の立ち上がりのタイミングで遅延が大きいことがわかる。周波数を上げなくても入力の立ち上がりでトリガーして掃引を速くしていけば同じ様に出力の立ち下がりが遅れているのが見える。この遅れは一定なので周波数が高くなる度に一定時間内の比率が大きくなりFETで損失する電力が比例して増える。  急激な貫通電流パルスの影響でブレッドボード基板の電源配線インダクタンス分で昇圧回路となり電源より高い電圧が出力に出てきている。電流制限抵抗を入れないと安定化電源の最大出力電流まで流れてしまう(ほぼ短絡と同じ) これはPチャネルとNチャネルで特性が異なるためで違いにコンプリメンタルなペアを使用すれば貫通期間は最小限になると思われる。 ううむ一筋縄ではいかないか。 |

| フラット表示 | 前のトピック | 次のトピック |

| 投稿するにはまず登録を | |