| フラット表示 | 前のトピック | 次のトピック |

| 投稿者 | スレッド |

|---|---|

| webadm | 投稿日時: 2006-7-29 21:59 |

Webmaster   登録日: 2004-11-7 居住地: 投稿: 3088 |

貫通電流を観測してみた どんな感じで貫通電流が発生しているか見てみた。

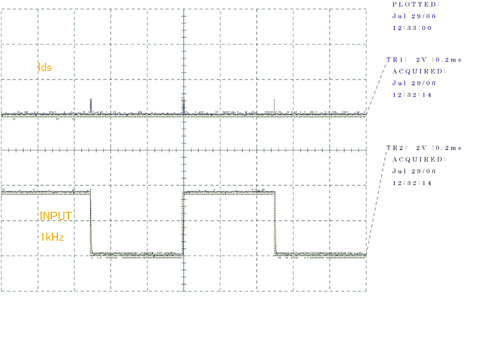

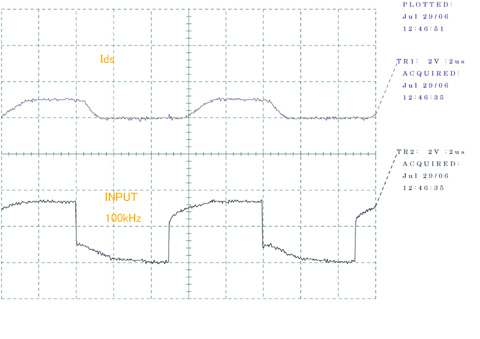

といっても電流はオシロでは観測できないので、電流制限抵抗10オームをNチャネルMOS FETのソースとグランドの間に入れてその両端の電圧を観測することにした。  1kHzではこんな感じで出力の立ち上がりと立ち下がりの時に貫通電流がパルス的に発生している。この状態では貫通電流は10オームの抵抗で1v程度出ているので100mAぐらいと推測される。単位時間当たり電流が流れている時間は短いのでFETは熱をもたない。 更に入力周波数を上げていくと入力パルス幅が段々と狭くなるにつれて出力の立ち上がりと立ち下がりの間隔が狭まりついには二つの貫通電流パルスは連続してしまう。  ほぼ5割の時間が貫通電流が流れている。安定化電源の電流計は平均値である50mAを示している。この程度であればまだFETはほんのり暖かい程度。 ただこれも電流制限抵抗が入っているので流れる電流のピークが抑えられているものの、そうでないと更に周波数を上げていくと比例して電流も増えていく。電流制限抵抗があるとローパスフィルター効果で特性が悪くなり出力波形が相当鈍るので電流が増えていくというのは100kHzぐらいまででそれ以上になると逆に出力状態が変化しなくなり電流は減っていく。 シミュレーションでも電流制限抵抗をほんのわずかでも入れただけで特性が悪くなることは確認済み。 教科書に書いてあるような単純なCMOSインバーター回路ではちょっと役にたたないということが判明してきた。別の回路を実験してみる必要がありそうである。 |

| フラット表示 | 前のトピック | 次のトピック |

| 投稿するにはまず登録を | |