| スレッド表示 | 新しいものから | 前のトピック | 次のトピック | 下へ |

| 投稿者 | スレッド |

|---|---|

| webadm | 投稿日時: 2006-3-20 1:00 |

Webmaster   登録日: 2004-11-7 居住地: 投稿: 3094 |

デザインのウォーミングアップ仕上げ 先の簡単なジャンケン判定装置は論理回路設計では序の口でまだ本格的なものではない。ウォーミングアップはまだ始まったばかりである。

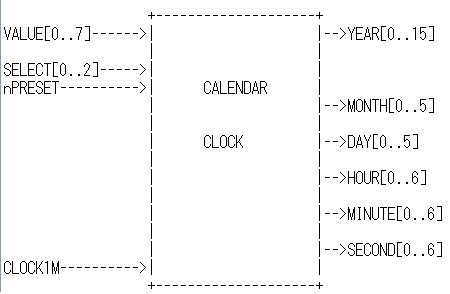

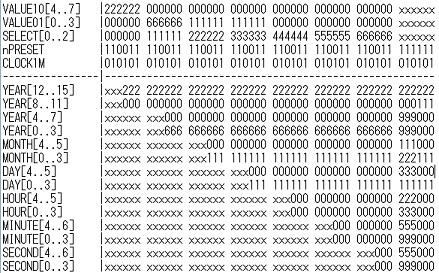

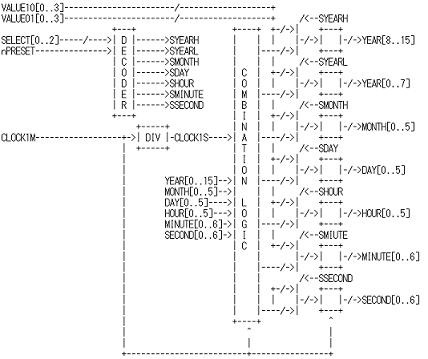

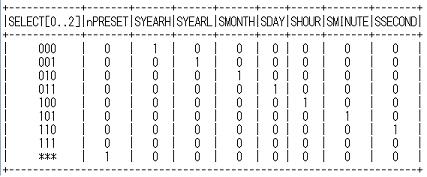

今度は本格的なディジタル回路であるステートマシンのデザインを練習することにする。 題材はいくらでも転がっているが、いきなりコンピューターシステムの一部に目を向けても興味が失せるので、現実世界と親和性のある題材を探してみた。 そこで思いついたのが万年カレンダー時計である。 仕様をざっと書いてみる。 1MHzのクロック信号と時計あわせのためのプリセット信号を入力でき現在の年月日時分秒を出力する。 年月日時分秒値のプリセット値入力はロータリースイッチ等を接続することを前提にBCD値入力とする。 出力はそれぞれBCD値出力とする。閏年をサポートする。西暦1万年問題は考慮しなくてよい。 ブロック図は以下の通り。  入力信号数16ピン、出力信号数45ピン。合計信号61ピン。 代表的なタイミングチャートは以下の通り。  仕様策定段階でEPF8282LC84の最大user i/oピン数64ピンの制約に収まるようにプリセット入力を2桁ずつ選択してセットするようにしてピン数を節約。 直接7セグメントLEDを駆動させようとすると出力1桁あたり7本ピンが必要になるのでピン数は収まらないため7セグメントデコーダーを内蔵することは断念。 カレンダークロックはステートマシンの中では状態数が非常に多いのですべての状態についてタイミングチャートなり真理値表を書くことは現実的ではない。 従って代表的なプリセットと年替わりのケースを示すにとどめた。 ステートマシンでは仕様策定段階で既にそれを実現するために必要な構成回路要素をあらかじめ知っている必要がある。当然ながらその設計者も同水準の知識を有する必要がある。 仕様的には簡単に見えるが、実際に実現することを考え始めると様々な選択枝があり簡単では無いことがすぐわかる。 ステートマシンをデザイン入力するに先だってまず全体を複数の小ブロックから構成するように機能分割する必要がある。 仕様設計者は時計合わせのために必要な入力ピン数を節約するために設定項目をローターリースイッチでバイナリ値として入力するようにしている。 実際には該当する内部変数(ラッチ)をプリセットするために内部でバイナリ値をデコードすることを前提としている。 バイナリデコーダーがどんなものかをあらかじめお互いに知っていることが前提になる。 また内部変数(ラッチ)はプリセット時以外は毎秒次の秒までの間表示すべき値を保持すべく更新される。 このためプリセットには外部入力信号をそれ以外は内部信号を入力するように切り替えるデータセレクタが内部に必要になる。 バイナリデコーダーもデータセレクタも基本的な組み合わせ論理であるため真理値表や論理式で記述することができる。 あとは内部変数(ラッチ)を毎秒更新するための組み合わせ論理を考える必要がある。それと1MHzのクロックから秒クロックに分周する回路が必要である。 これらをブロック図に描くと以下の通り。  DECODERはnPRESET信号がアサートされている間だけSELECTバイナリ値をデコードし該当するデコード信号のみアサートする。 各デコード信号はそれぞれ該当するラッチの入力をCOMBINATION LOGICかVALUE入力かを切り替えるデータセレクタの入力となる。 DIVはCLOCK1Mを分周してCOMBINATION LOGICが次の時刻を更新するのに使用する1秒周期のクロックを生成する。 COMBINATION LOGICは1秒クロックとラッチの前回値を入力として更新時刻を出力する。 更に詳細に各ブロックの仕様を設計する。 DECODERは組み合わせ論理で以下の真理値表で表すことができる。  DIVは単純な分周カウンタ。 COMBINATION LOGICは複数の組み合わせ論理から構成されるもっとも複雑な部分。 分替わり、時替わり、日替わり、月替わり、年替わりには様々な条件が加わるため簡単ではない。 秒の更新は一番簡単で0〜59までは1秒毎に1ずつ増加し59から60に増加するタイミングで0に戻す。 秒が0に戻った際に分替わりのため分の値を1増加させる。59から60に増加するタイミングで0に戻す。 分が0に戻った際に時替わりのため時の値を1増加させる。23から24に増加するタイミングで0に戻す。 時が0に戻った際に日替わりのため日の値を1増加させる。この場合、現在の月の最終日から増加するタイミングで1に戻す。 日が1に戻った際に月替わりのため月の値を1増加させる。最終月から増加するタイミングで1に戻す。 月が1に戻った際に年替わりのため年の値を1増加させる。 月の最終日は2月を除いて各月によって31か30のいずれか。2月の場合は、現在の年が閏年か否かによって28か29となる。 年が400で割り切れる場合は閏年。その他の年で100で割り切れる場合は閏年でない例外がある以外は4で割り切れる年が閏年。 閏年の2月は29日が最終日となりそうでなければ28日が最終日。 一番難しいのが閏年の判定に割り算が必要なことである。割り算は組み合わせ論理では実現できない。 良く考えると4で割り切れるかどうかは、年のBCD4桁の一桁目の下位2ビットが共に0かどうかで判断できる。 100で割り切れるかどうかは、下2桁が共に0かどうかで判断できる。 400で割り切れるかどうかは、下2桁が共に0でかつ上位2桁が 00,04,08,12,16,20,24,28,32,36,40,44,48,52,56,60,64,68,72,76,80,84,88,92,96 の場合だけに限られる。これなら力ずくで条件判定すればできなくもない。きっとデザインツールがいまいこと論理圧縮してくれるに違いない。 これでおおよその設計情報は出そろったので次はHDLを書いてみることにする。回路図入力はできないことはないが体力が無いのでご容赦を。 |

| webadm | 投稿日時: 2006-3-20 21:10 |

Webmaster   登録日: 2004-11-7 居住地: 投稿: 3094 |

仕上げた結果 HDLでの入力自体は半日もかからなかった。その中でも時間を要したのは各月の最終日がどうだったか調べるのに費やされた。

一年の前半は奇数月が31で偶数が30日だけど後半は偶数が31日で奇数が30日だとはすっかり忘れていた。あと今年が閏年でなく2月の最終日が28日なのを先月のカレンダーで確認。 階層的に記述する仕方を知らないこともあって、一枚岩になってしまったので仕様検討段階で思い描いていたような見通しのよいものとはかけ離れてしまった。やっていることは等価であるが。 いろいろ文法とかいきあたりばったりで書いているのでコンパイルエラーをとるのに少々時間がかかったものの、躓くことはなくコンパイルはすぐ通るようになった。 問題はここからでシミュレーションのためにプリセットのためのテストベクターを与えなければいけないのだがその方法が後になるまでわからなかった。仕方がないのでとりあえず0000年00月00日00分00秒から時計が進むかどうかを確認してみた。この時点で1MHzクロックを分周して1秒を数えるのが気の遠くなる時間だということが判明。急遽クロックを2Hzに落とすように勝手に仕様変更。ふつうは32.768KHzで十分だということに気づく。 それでもさすがに年替わりまで見ることはできないものの、この段階でいくつか記述上の抜けから繰り上がり後に値が保持されないとかの問題を発見。本当はもっとエレガントな記述方法があるのだろうと思うけど、行き当たりばったりで行を追加。 万年時計のAHDLソース 翌日にすっきりした頭でデザインツールのヘルプドキュメントを読み直したらWaveform Editorで任意の波形パターンを入力する方法が判明。さっそくそれを使って仕様検討段階で描いていた代表的なタイミングチャートを試してみる。ちゃんとうごくじゃないか。 代表的なタイミングチャート ついでに最大の関心事だった閏年判定をチェックしてみる。まずは2000年は閏年なのでその2月29日の日替わりをチェックしてみる。ちゃんと3月1日に替わってくれた。 2000年の2月29日の日替わり 追加で今年は閏年ではないので2月28日の日替わりをチェック。これも問題ない。3月1日に替わった。 今年の2月28日の日替わり コンパイラーのレポートを見るとI/Oピンはもうだいぶ残り少ないもののLEは半分近くまだ手つかず。まだまだ機能を追加できる余裕がありそうである。nPRESETの他にnUPとかnDOWNとかを追加して指定桁を進めたり戻したりする微調整機能をつけてもよさそうである。これは読者の課題に。合成されている組み合わせ論理がどうなっているか気になるところだが、それほどの量ではないもののちょっと目ではどうなっているのか時間をかけないと読み取れない。 万年カレンダーのFPGAマップレポート 今回少し規模が大きいので遊んでみた感想はいろいろあるものの書ききれないのでまた後日。 |

| webadm | 投稿日時: 2006-3-21 23:10 |

Webmaster   登録日: 2004-11-7 居住地: 投稿: 3094 |

仕上げの感想 今回はHDLだけで万年時計のデザインをしてみたわけだが、3日もあればできてしまったのは驚きだ。若けれは夜を徹してやれば1日できるだろう。

さすがに回路図入力しようという気はさらさらなくなった。というのも回路図入力しようとするとHDLを使えばデザインツールがやってくれる論理ゲートのネットリストに落とす作業をある程度までは人力でやらないといけないからだ。 バイナリデコーダーやラッチとかはたいしたことないが、残りの組み合わせロジック部分が膨大になる。得にBCDのカウンターとか加算回路が必要だし、閏年判定とかに至っては真理値表が膨大になってしまう。その結果入力しなければならないゲート数も膨大に。それでも基礎力があればできないことはないだろう。でも回路図も膨大になって修正をするとなると時間がかかって大変だ。修正後に関係ない信号線どうしがくっついてしまっていないか導通確認の時間もばかにならない(信号線をダブルクリックすればつながっているすべての信号線がハイライト表示されるので面倒ではないが、回路図CAD特有の問題ではある)。 実際に回路図入力すると前にやった簡単なジャンケン判定の時も意図せずして違う信号線がショートしてたり予想もしないことがおきたので回路図入力は結構落とし穴がある。修正した時に配線が変なことになってしまうこともしばしば。おかしなシミュレーション結果が出るたびに結線状態を全チェックするはめに何度もなった。 HDLだともうほとんど真理値表やそれに相当する入力条件と出力の因果関係を決定した後の論理合成はデザインツールがやってくれる。なので回路図入力に比べてかなりの手抜きができる。反面どんな回路が合成されたかは謎でブラックボックス化するが。 そんなことを改めて確認したところで、よく「FPGAですか...回路図入力ならできますがHDLはちょっと...」とぼやく一応H/W設計畑の経歴を持つ働き盛りの技術者を目にしてずっと疑問に思っていたが、ようやく結論が出た。彼らは、(1)はなはだ怠慢である、(2)本当は独力設計した経験がない、(3)誰かが書いた回路図を元にデザインツールにインプットしたことはある、(4)今までは誰かが設計した回路のメンテナンスやテストばっかりやらされていた、のいずれかだろう。本当に回路図で設計した経験があるなら(1)が該当するとしか言えない。いずれにしてもそういう人を採用しないのが正解だ。 やはりFPGAの難しいところは、ある程度はFPGAが登場する以前のプリミティブなディジタル回路技術については一通り知識を持っている必要があるということだろう。あとは組み合わせ論理はすべからくNANDとNORのネットリストかROMテーブルで表すことができ、それにラッチを組み合わせればどんなディジタルシステムもできてしまうということ知っていればもう怖くはない。設計者はFPGAにマップされるネットリストの元になる情報を準備すればOKである。 それ以降はいかに完全な設計情報を事前に用意できるかどうかで後の作業(シミュレーション結果の確認)で生じる後戻りが少なくできる。人間なので見落としや検討不足、間違いや勘違いが伴いやすいので、結局はそうした自分の墓穴をひとつひとつ埋めていくことに残りの時間は費やされる。 今回万年時計の仕様を考える上で最初7セグメントLED表示器をつけるはずが信号ピンが足らなくてBCD出力にしてしまったのだが、あとから良く考えるとダイナミック点灯方式を使えば少ない出力ピン数で複数の7セグメントLED表示器を表示させることが可能だということを思いつき失敗したなと思った。そういえばどっかでダイナミック表示方式の回路図を見た覚えがあった。ダイナミック表示とは人間の目の残像時間を利用して同時期にはひとつしか点灯させないが、残存時間無いに複数の表示器を順番に点灯と消灯を繰り返していくことで人間の目には全部が表示されているように見えるというものである。 ここまでいくとやっぱり実際に実機を作ってみたくなる。 そういえば昔ミニコンピュータの時代の頃、カレンダークロック装置というものが別についていた。ミニコンピューターには今のPCのようにカレンダー時計ICが搭載されておらず、電源を入れ直すとシステムを構築した日付にリセットされてしまい、人間が日付を設定しなおす必要があった。組み込みシステムとかでは無人で動作しないといけないので、各社各様の自前のカレンダークロック装置を取り付けてソフトウェアで時刻合わせしていたのである。あれは確か99年までしか表示がなかったから2000年問題はどうしたのだろう、ミニコンのOSも99年までしか扱えなかったはずだ。そういうミニコンを作ってたメーカーは2000年以降どれも生き残っていないのはそれが原因かもしれない。 あと些細な点で、MAX+PLUS IIのシミュレーター結果でDFFとしたはずの出力がクロックの立ち上がり以外のところで変化しているのが気になった。DFFならクロックのエッジで入力を取り込みあとは変化しないのではなかったはずだ。まるで出力スルーラッチのような感じだ。どうやらそう考えるのがあたっているようである。BCDのビット繰り上がりが発生するときにCLKがHの状態でその繰り上がりの様子を示すように出力が変化している。CLKがLの状態では出力は変化していないのでそれで説明がつく。これは実際にそうなのかシミュレーション時だけの手抜きなのかは実機で動かしてみないとなんとも。 今回は実機でどれも動かしていないので動くとは思うが保証の限りではない。 とにかく今はデザインツールが登録するだけで無償で使えるので勉強するには良い機会だ。シミュレーションができるので実際に評価基板とか無くてもかなりのトレーニングは独学でできる。もちろんお金を払えば、短期間に水先案内人付きで使い方を教えてくれるコースもある。 雑誌に評価基板を付録でつけるひつようは無いという意見があるのはごもっともなことろ、シミュレーターがあれば勉強には十分な気もする。けれどもそれは年寄り的な発想であることも確か。やっぱり実物を目にするまでは潜在していた何かが目覚めることもないことも確かである。 尊敬するApple IIの設計者であるスティーブ・ウォズニアック氏も展示会で6502の無料サンプルを手にして初めてApple Iを作る衝動にかられたのだし。そうした夢を与える機会は大切にしたい。 |

| webadm | 投稿日時: 2006-3-22 22:05 |

Webmaster   登録日: 2004-11-7 居住地: 投稿: 3094 |

7セグメントLEDデコーダー内蔵版もできた 昨夜は眠れなかったので、7セグメントLEDデコーダーを内蔵した以下の仕様で万年時計をバージョンアップしてみた。

7セグメントLEDデコーダー内蔵万年時計の仕様 やっとこさツール付属のヘルプドキュメントを見て階層構造にする方法が判明。結局以下の7セグメントデコードロジックをsubdesignとして書いてCreate Default Include Fileというのでデザインをコンパイルすると.incというファイルができるのでそれを上位のsubdesignでインクルードするだけでそのインスタンスが使えるようになるだけだった。以下は7セグメントデコードロジックのsubdesignソース(bcddecode.tdf)。 引用:

以下はツールが生成したincludeファイル(bcddecode.inc)の内容。 引用:

7セグメントデコーダーを内蔵してダイナミック点灯方式の万年時計のデザインは以下の通り。 ダイナミック点灯方式の万年カレンダー(calendar2.tdf) 今回は実際に実機で動かしてみることを念頭にパラメータでクロック分周比やダイナミック表示の点灯時間を調整できるようにしてある。 ダイナミック点灯方式のシミュレーション結果 FPGAのコンパイルレポートを見るとさすがに7セグメントデコーダーとかダイナミック点灯のためのカウンターとかを追加したためにLEの使用率が91%に上昇しています。 ダイナミック点灯方式のFPGAコンパイルレポート あとは7セグメントLEDをドライブするための部品とそれを載せるためのユニバーサル基板とコネクタを調達すればFLEXデザインキット/CQと接続して動作が確認できそうな雰囲気。 いずれトラ技の付録についてきたMAXIIとQuartusIIでVerilog-HDLやVHDLバージョンも試してみたいところ。 |

| webadm | 投稿日時: 2006-4-2 2:14 |

Webmaster   登録日: 2004-11-7 居住地: 投稿: 3094 |

いよいよ製作開始と思ったら なんとか周辺回路図を書き上げて必要な部品も発注したものの慟哭の事実が判明

FPGAの信号ピン割り当てを確認していたところ矛盾を発見。よく見たらEPF8282ではなくてEPF8452にデバイスがアサインされていた。 自動デバイス選定になっていたのでLEが不足してピン数は同じだがLE数が一回り多いEPF8452にすり替わっていた。 さすがにどうがんばっても必要LE数を減らすのは今更難しい。 とするとEPF8452を入手してそれを実装した専用基板にしてしまおうかと考えたが、若松通商にはEPF8282の在庫はあってもEPF8452は置いていない。EPF10Kなら84pinのが入手可能なもののMax+plus IIでは扱えない。少なくともマッピングするのにQuartus IIを使わないといけない。 ということでFLEX10Kをプログラミングするためにも最低でもプログラミングケーブルが必要になってしまった。CQ基板のプログラミング回路を使ってもできると思うがソフトウェアがどうもFLEX8000を前提にしているところがあるので変更しないといけない気がする。実装はPLCC 84pinだからなんとかなるはず。 |

| webadm | 投稿日時: 2006-4-2 2:48 |

Webmaster   登録日: 2004-11-7 居住地: 投稿: 3094 |

Max+plus IIでもFLEX10Kは使える ふとだめもとでデバイス指定のリストを開いてみたらFLEX10Kがあるではないか。

設定してコンパイルしてみたら、Quartusテクノロジーを使用とかいう経過メッセージが出てちゃんとコンパイルできた。 84pinのEPF10K10LC84に余裕で収まった。 これでFLEX10Kボード製作決定。 |

| webadm | 投稿日時: 2006-4-9 1:01 |

Webmaster   登録日: 2004-11-7 居住地: 投稿: 3094 |

先行手配した部品が届いた 若松通商に部品を発注してからFPGAがフィットしないという重大ミスが発覚し会社なら始末書ものだけど、FLEX10Kの基板を作ることで決着。

最初に発注した7SEG LEDやらトランジスタとかの部品が届いた。 あとは新たに起こすFPGA基板の回路図を作成して必要な部品をまた発注することに。本当はFPGAの載っていない基板だけあればいいのだけれども。 これだけ7SEG LEDが並ぶものは見たことが無い。いや映画Back to the futureのデロリアン号にあるタイムマシン設定パネルでみたかも。 |

| webadm | 投稿日時: 2006-4-15 21:30 |

Webmaster   登録日: 2004-11-7 居住地: 投稿: 3094 |

FPGAまわりの回路図作成にとりかかる FPGA周りの回路図を書かないと追加の部品発注がいつまでたってもできないのでとりかかることに。

とりかかるとすぐにFPGAのコンフィグレーションの仕方について良くわかっていないことが発覚。ALTERAのサイトをいろいろ見ても情報が散在していてよくわからず。プログラミングケーブルを使用してコンフィグレーションする方法は参考になる回路とかはあるものの、プログラミングケーブルを使わずに自動で電源投入後にコンフィグレーションデバイスを使用しておこなう方法についてはFPGAの進化とともに変化しているらしく鬼門らしい。 汎用的な実験用FPGA子基板を作ろうと思うのでコンフィグレーションデバイスかプログラミングケーブルかどちらでもコンフィグレーションできるFPGAだけ乗った基板にしたいが、さてどんなコンフィグレーションデバイスチップを使えばいいのやら。 ALTERA Configuration Deviceという資料を読むのが基本らしい。それによると再プログラム可能なコンフィグレーションデバイスとそうでないワンタイムのがあるらしい。最近のFPGA用のものはほとんど再プログラム可能なもので、一部の古いもの(EPC1,EPC1441)がワンタイムらしい。あとは末尾の数字(EPCx)がどうやら記憶容量(Mbit)に対応するらしい。 今回使用する予定の古いFLEX10K10だと対応表からみると容量的にはどれも十分である。再プログラミングして使えるもので手頃なのはEPC2ということに落ち着く。 FLEX10K用のEnhanced Programming Deviceの資料リンクをたどるとそれはEPC4,8,16という大容量のものしか載っておらずはずれ。 別のところにConfiguring Mercury,APEX20K(2.5v),ACE 1K & FLEX10K Devicesという資料があり、それに使い方が書いてあった。MercuryとはFLEX10Kを含む当時のALTERAの大容量FPGAのコード名らしく、容量が違う以外は同一のコンフィグレーション方法を用いるらしい。この当時はFPGAをデイジーチェインして1つのコンフィグレーションデバイスでコンフィグレーションする方式だったようだ。 結局はFLEX/CQ基板や他で見つかるFLEX10K基板とかにあるようにプログラミングケーブルのピンとパラレルにコンフィグレーションデバイスのソケットを接続しプログラミングケーブルかコンフィグレーションデバイスのどちらか一方を差し込むというごくあたり前のことだった。あとFLEX10KはJTAGでもコンフィグレーションできるがこれはPSモード用とは別のJTAG用信号ピンを結線したヘッダピンを用意すればよいらしい。一応PSモードとJTAGモードどちらも試したいので二つ10pinヘッダーを用意することになる。 だいぶ寄り道したけれどもしっかりと公式の資料に基づいて設計するのが大事だ。 |

| webadm | 投稿日時: 2006-4-15 23:38 |

Webmaster   登録日: 2004-11-7 居住地: 投稿: 3094 |

部品ライブラリから作らないといけない さっそくFPGAまわりの回路図を書いてしまおうとEAGLEを立ち上げて部品をAddしようとライブラリ内のaltera.lbrのところを開く。

しかしFLEX10K10-P208というPQFP208pinのはあるが、それより小さいパッケージのものが見あたらない。 どうやら自分で作るしかないようだ。 そういえば国産のバイポーラトランジスタ用のライブラリも無いのでTO92-ECBというパッケージも見あたらないので作る必要があったのだけれども面倒なのでやってなかった。 幸いパッケージはPLCC84があるので作る必要はないものの、84ピンタイプのFLEX10K10の回路図シンボルを作成して信号ピンをパッケージにアサインする作業はやらないといけない。 さてシンボルを作成するのにはどうしたらいいものか、以前に見つけた趣味の電子工作サイトでEAGLEのライブラリ作成の仕方が紹介されているのでそれを読み始める。 |

| webadm | 投稿日時: 2006-4-19 0:31 |

Webmaster   登録日: 2004-11-7 居住地: 投稿: 3094 |

あともう少し 部品ライブラリーは見よう見真似でそれらしいのが作れることがわかった。けれども既存のALTERA用の部品ライブラリーをまねてもIC直付けだったりするのでpackageをPLCC84じゃなくてsocket-plcc.lbrの中にある84pin PLCCソケットのやつをコピーペーストしなければならないことに出来上がった後気づく。

いちど要領を覚えれば新しく作りなおすのは簡単であった。 とりあえずFPGAとピンヘッダを結線する回路図を作成してボードに並べてautorouterで配線してみると、今まで見たこともないほど配線完了まで時間がかかった。眺めていると一度仮配置して残りの配線がうまくいかないとわかると仮配線からまたやり直すというのを何度か繰り返して最終的に収束している。 ピンヘッダの信号アサインはLED基板をFLEX/CQ基板で動作チェックできるようにとピンコンパチブルにするためちょっと変則的になってしまった。EPF10K10専用ならビアが最少数になるような最適な信号アサインも可能なのだけれども、今回も手配線なので関係なし。 あと残っているのはコンフィグレーション用の回路で、そこでまたしても疑問が発生。検索でみつけたいろいろな回路ではコンフィグレーション信号のpull upやpull downの仕方はまちまちなのを発見。抵抗値についても1Kのが多いが4.7kとか中途半端なものもあったりする。 もう一度ALTERAのコンフィグレーション関係の資料を詳しく読み直すことにした。それによると一部のコンフィグレーション用出力信号ピンはオープンドレインであることを知る。複数のFPGAをコンフィグレーションするのにパラに接続する必要があるからだと納得。それなら1Kぐらいにしないと立ち上がりがなまるのは確か。電流制限的な意味で1Kというところなんだろう。 あとJTAGのTCLK信号がpull upしているものとpull downしているものがあってどっちが本当だろうと疑問になった。これも調べるとALTERAの資料では1kでpull downせよということになっている。FPGAに電源が入ると内部リセットが解けた時点でJTAGは使用可能になるのでTCLKの立ち上がりが誤って発生するとFPGA内のJTAG TAPコントローラのステートが進んでしまい誤動作につながるのであらかじめpull downすれば立下りは発生しても立ち上がりは生じないことになる。 pull up抵抗値についてはCycloneの資料では10kと大きく異なっている。これはCycloneのコンフィグレーション方式がASモードとそれ以前のFPGAと異なるためだと思われる。JTAG indirect configurationなんかもCyclone特有のものらしい。当面Cycloneのことは心配しなくてもよさそうである。 |

| (1) 2 3 4 5 » | |

| スレッド表示 | 新しいものから | 前のトピック | 次のトピック | トップ |

| 投稿するにはまず登録を | |