| スレッド表示 | 新しいものから | 前のトピック | 次のトピック | 下へ |

| 投稿者 | スレッド |

|---|---|

| webadm | 投稿日時: 2006-5-18 16:01 |

Webmaster   登録日: 2004-11-7 居住地: 投稿: 3094 |

ウォーミングアップ後のテーマはJTAG Waveform emulator(中止) とりあえず10年以上の時代の流れに追いつくためのウォーミングアップは悲惨な結末にならずに済んだのでよしとしよう。まだ数年前に追いついた感じだし、作ったFPGAボードもJTAGとクロックオシレーター搭載時にコンフィグレーションエラーが発生という未解決の謎が残っているが深追いするとまた病気になって1しまうので追々やることにして次の挑戦テーマを見つけることにしよう。

といってもいきなり実用的な課題だと問題解決のための理論的落とし込みがたいへんなので、やることはすべて既知かどっかに書いてあるがFPGAではだれもやらないだろうことをやるのがおもしろそうだ。 今回JTAGで躓いたのとロジアナやストレージオシロがないため解析に窮したこともあってJTAG Waveform emulatorなるものを作ることにしよう。いきなり本格的な設計からではなく基礎的な知識の確認を積み重ねながら最終的に仕様へ落とし込むことからはじめる。 このアイデアはトラ技付録のCPLD基盤とMITOUJTAGトラ技評価版のEXTEST機能を使った時に発案したのだがMITOUJTAGのそれはマウスでクリックという取っつきやすいマニュアル操作しか用意していないので大変残念だった。もしMITOUJTAGにWAVEFORM editor付きの本格的なEXTEST機能があれば作ろうとは思わなかっただろう。 他の人と競合もしないのでこれに決めた。 |

| webadm | 投稿日時: 2006-5-19 22:04 |

Webmaster   登録日: 2004-11-7 居住地: 投稿: 3094 |

まずはJTAGの標準規格書を入手することから 最新のFPGA/CPLDはどれもほとんどJTAGというかIEEE 1149.1やIEEE 1532という規格に準拠してきた。それ以前からJTAGの元祖であるバウンダリースキャンというテスト容易化技術はディジタル系の半導体屋さんではそれ以前から各社独自方式で実用化されていた。もちろんそちらは社外機密。

JTAGはそうした各社各様のバウンダリースキャン回路の方式を業界で統一して共通化しようという動きによってできたと思われる。現在ではそのおかげで北米とかではJTAGやバウンダリースキャン関連の受託開発やパッケージ製品開発でいくつもの会社が出来ているぐらいメジャーな技術。 FPGA/CPLD以外のデバイスでもARM/PowerPCなどのRISCプロセッサコアもJTAGを採用してデバッグとかが行えるようになっている。どちらかというと国内ではこちらの用途が良く知られているかもしれない。JTAG以前のデバッガというとICEとかいう前時代的なものがあったけどあれは考えてみればCPUチップの周りに自前でバウンダリースキャンロジックをつけたようなものだった。CPUにはじめからそういう機能が入っていればそういったものは無用になってしまう。 前置きが長かったが、JTAGをいじるにあたってはちゃんと規格を勉強しないとはじまらない。一番近い原典を読むのが筋である。 JTAGの規格書は市販されている。といっても国内で扱っているところがあるかどうかは不明だが、IEEEに行けばインターネットで購入できる。有償だが国内の規格書みたいにべらぼうな値段はとらない。http://www.ieee.org でStandardというところをひらいてbuy standardで検索すればそのままご購入ができる。古いものは印刷したやつとPDFの二種類があるので注意。PDFを購入すれば即日ダウンロード可能になる。印刷したのは郵便で送られてきてしまうので同じぐらいの輸送量がとられたあげく東京在住なら石原都知事のおかげで消費税までとられてしまう。今回購入したのは以下の2つ。 Product: "Standard: 1149.1-2001"(Revision of IEEE Std 1149.1-1990) IEEE Standard Test Access Port and Boundary-Scan Architecture"" consists of the following files. 1149.1-2001.pdf Product: "Standard: 1532-2001"IEEE Standard for In-System Configuration of Programmable Devices"" consists of the following files. 1532-2001.pdf 二つ合わせても$151(IEEE会員価格だが非会員でもそれほど変わらない) さてこれから一通り目を通すことにする。 |

| webadm | 投稿日時: 2006-5-20 3:59 |

Webmaster   登録日: 2004-11-7 居住地: 投稿: 3094 |

とりあえずざっと読み終えた 早すぎ

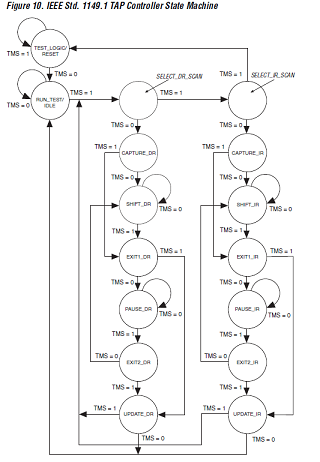

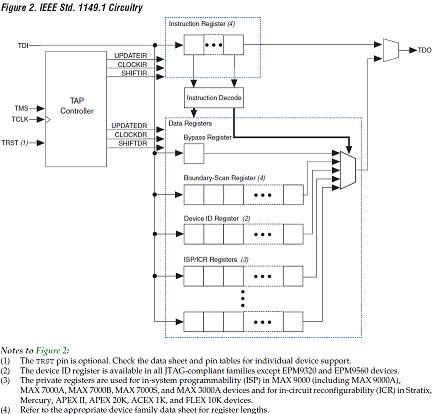

といってもIEEE 1149.1の内容はALTERAの資料にも出てくるJTAG TAPコントローラーの状態遷移やデータレジスタの説明、それらの実装方法、それにBSDLファイルの仕様が付録でついているだけであった。作成された年代が古いので状態遷移図とかはカメラで取り込んだようなFAXみたいな状態でよく見えない。ALTERAの資料にある図のほうが大きくてはっきりして見やすい。IEEE 1532はこれはJTAGを使ったISPに関する規格なので今回はとりあえず不要。プログラムする時は必要になるが、大変複雑で難解であるとだけ言っておこう。 IEEE 1149.1はALTERAの資料にある以下の図   を眺めれば賢明な読者であればその機能と動作や使い方についてある程度読み取れてしまうので、あえて規格を読み直す必要はないかもしれない。でも後半に書かれている実装方法についての記述はJTAG TAPコントローラーがいかにデリケートなものであるかを理解するのに役立つ。作るにもクロックの立ち上がりと立ち下がりの両方のエッジで動作する回路になるため、いきなりノンオーバーラップクリッキングとかを使うことになるので初心者には敷居が高すぎる。 どうりでJTAGはTCKの波形をきれいにしないとまともに動かないわけである。普通のクロックは立ち上がりがきれいなだけでよかったがJTAGは立ち下がりもきれいでないといけないし、のろのろとしていてもいけない。JTAG TAPコントローラ内部で立ち上がりと立ち下がりに同期して立ち上がる2つのクロックがちゃんと生成されないとたちまち誤動作につながる。 しかしそれにしても我がFLEX10Kボードは何故にJTAGが誤動作しまくりなのか、それは追々実験しながら明らかにしていこう。それも目的のひとつ。 |

| webadm | 投稿日時: 2006-5-21 20:15 |

Webmaster   登録日: 2004-11-7 居住地: 投稿: 3094 |

Jam STAPL Player他 JTAGをいろいろ試すには最低限JTAGケーブルがあればソフトウェアでTCK,TMS,TDIを操ってTDOを読み出すのが一般的である。

JTAGケーブルはALTERAやXILINX、LATTICEなどがそれぞれ独自の仕様のものを売っていたり仕様をある程度公開しているので買うか自作することが簡単にできる。 しかしソフトウェアになるとちょっとゼロから作るのは誰にとってもハードルが高い。何が正しいのかわからないし、ケーブルやターゲットの回路の相性とかでうまく読み出せない時にはなおさら出口の見えない泥沼に入ることになる(既に経験済み) そこで誰か最初にそういうソフトウェアを書いた人がいればそれを公開してくれればだいぶ敷居が低くなると誰しも考えるはず。 実はそういうのが世の中にはいくつかある。中でも信用がおけるのがALTERAがJTAGの基本的な操作がプログラムできるJam STAPL PlayerというBASIC風の言語(STAPL)インタプリターをソースコード付きで公開してくれている。サポートしているJTAGケーブルはALTERAのパラレルケーブル(ByteBlaster系)とシリアルケーブル(BitBlaster)、XILINXやLATTICEのJTAGケーブルなどと気が利いている。どれかひとつもっていればよいことになる。 Jam STAPL PlayerはSTAPLで書かれたテキストソースかあらかじめコンパイルされたバイトコードのどちらでも実行できる。STAPLのコンパイラも別途提供されていてALTERAのサイトからダウンロードすることができる。 それとSTAPLで書かれたサンプルソースもあるので、実際に実行して試してみることができる。今回はIDCODEというデバイスIDを読み出すプログラムを実行してみた。これは新しく作ったFPGA/CPLDボードでJTAGが正しく機能するかテストするのに有用である。というのも最新のデザインツールとかはJTAGの操作が失敗しても詳しいトラブル解析のための情報はほとんど表示してくれないので、試作したボードの設計がまずかった時にはお先真っ暗になる(既に経験済み) 実際に今回自作したFLEX10KボードでIDCODEを試してみた結果は以下の通り。 引用:

インチキケーブルやインチキボードで同じことを実行すると以下のようにエラーに遭遇しその原因が表示される。 引用:

もちろんJam STAPL PlayerはIDCODE以外にもほとんどすべての標準のJTAG命令を利用したバウンダリースキャンテストをプログラムすることができる。なのでJTAGが誤動作する原因を探る場合には利用することができる。 今回のテーマではハードウェアで同様のことをやってしまおうという無謀な計画である。実際にどうJTAGを操作すればよいかはこのJam STAPL Playerをお手本にしてやってみることにする。 ALTERAからこのソフト以外は得に役立つドキュメントとかは提供されていないが、XILINXからはJTAGの基本的な動作やそれを使ったJTAGのトラブルシューティングに関する解説ドキュメント(JTAG Programmer Guid)が提供されている。それにはXILINXのJTAGケーブルの回路図も含まれている。それらも併せて読むとよりJTAGについて理解が深まると思われる。 |

| webadm | 投稿日時: 2006-6-5 3:14 |

Webmaster   登録日: 2004-11-7 居住地: 投稿: 3094 |

「バウンダリスキャン講座」発見 体を休めながら横になって検索していると、Freewingさんとこでデバッグソリューションのバウンダリースキャン講座というのが公開されているのを知る。

さっそく見てみると、JTAG規格の基本的なことがわかりやすく簡潔に解説されている。BSDLファイルに関しても別途解説があった。 自分の理解を確認するためにも良い情報だ。 そういえば昔CQ出版からJTAGに関する解説本が出ていたらしいがとっくに絶版になったとか。時期尚早だったのかも。今ではソフトのデバッグでは定番なのに。とはいえJTAGデバッグはあくまでJTAGベースなだけで実質的にはCPUアーキテクチャ毎に具体的なデバッグに必要な操作の手順は異なってくるのであまり勉強しても参考にならないか。 |

| webadm | 投稿日時: 2006-6-10 1:56 |

Webmaster   登録日: 2004-11-7 居住地: 投稿: 3094 |

読書中 すぐにでもJTAGの基本操作を行うステートマシンを書いてもよさそうだが、なんとなくつまらないので少し昔買い置きしてあった本をじっくり読んでいる。

「VHDL Analysis and Modeling of Digital Systems」McGRAW-HILL INTERNATIONAL EDITIONS,Electrical And Computer Engineering Series, Zainalabedin Navabi, ISBN 0-07-112732-1 10年前にVHDLを学ぼうと思って買ったまま病に伏してお蔵入りになっていたものだ。ペーパーバック版シリーズのひとつで2400円の値札がついている。安い。 最初のはしりの部分は長くHDLシミュレーターや論理合成ツールの研究に携わっている著者の背景から、今では誰も語らないVHDL誕生までの歴史が書かれている。このあたりは正しく技術を受け継ぐものならば読み飛ばせないところだ、おいしいところだけ分かればよいという潜りはさっさと読み飛ばしてしまい業界には根付かないだろう。 それが終わるとVHDLを構成する基本的な概念やキーワードの持つ背景や意味がまどろっこしいほど丁寧にかつゆっくりと解説されている。このあたりも著者独特なこだわりを感じる。普通はここはさっと通り過ぎるところだろうが、実はVHDLに限らずHDLを利用する者があらかじめ知っておかなければならない前提知識なのだ。 FPGA/CPLDやLSIをHDLで論理合成してシミュレーションするときには既にゲートレベルでのシミュレーションが可能だが、ターゲットプロセスが確定していない、ターゲットデバイスが確定していないもしくはFitingができない状態で論理を書いてテストする場合にはここのところをよく理解しているかどうかで結果が大きく違ってくるだろう。 代入や演算の評価順序や遅延を考慮することの重要性が読み手に伝わってくる。その上でようやくVHDLの基本概念がわかってくる。 そんな感じでゆっくりと高い山の裾野を歩いて登る感じで最終的にCPUを扱うまで隅々にわたるまでガイドしてくれている。ちょっと時間はかかるけどつきあって最後まで読んでみることにしよう。練習問題も豊富なので理解を確認するためには十分だ。 |

| webadm | 投稿日時: 2006-6-11 23:39 |

Webmaster   登録日: 2004-11-7 居住地: 投稿: 3094 |

読書完了 時代にキャッチアップするのは年月を隔ててしまうと永遠に追いつかないのではないかという不安感が常につきまとう。

半導体プロセスとかテクノロジーに依存する部分をVHDLではうまいことそれらに依存しないネットリスト的な構成要素と分離して記述構成できるように考えられていたということを理解。半導体プロセスやテクノロジーは日進月歩なので、既存の回路を新しいプロセス用のライブラリを使って構成してみたりというのがソースコードの最小限の修正で実現するというのが目的だろう。逆に言えば、ターゲットプラットフォームのタイミングとか遅延特性を前提としたトリッキーなデザインを書いてはいけないということにもなる。たまたま動いてもターゲットが変われば通用しなくなる。 読書が終わって再び修行のテーマに戻る。 つい昨日だったか以前から検索で一部ヒットして見たことがあるサイトに実はずいぶん昔からCPLDを使ったWaveform Generatorが公開されていたのを知る。ショックと同時に肩の荷が下りてほっとした気分。 JTAGこそは使っていないが基本的なfunction generatorは備えているのでちょっとしたアナログ回路の実験にはちょうどよい。 今回JTAGに自分が執着しすぎなのを反省したりもする。JTAGはTCK周りのアナログ的な配慮をすれば残りは純然たるディジタルなのでどうにでもなってしまうことは確かだ。ちょっとそこが寂しいところでもある。 別にJTAGよりもSPIとかいろいろある。難易度から言えばSPIとかのほうがずっと低い。JTAGはいろいろ詰め込むことができるだけに難解で扱いにくい。トラブルの際も解析が難しくなる。 ということで以前予想した通り古い小規模のFLEX/CQ基板はfunction generatorとして生き延びる道が残っていることは確かだ。既に万年時計で作成したLEDスイッチボードを流用してfunction generatorをこしらえることはできそうな気がする。 D/A変換はどうしようか、ものすごい抵抗ラダーとかで作るか市販のDACを使うか。 それとは別にJTAGの各種基本パターンを実行するデザインを考えてもよさそうである。表示を7SEGに行うとか。 |

| webadm | 投稿日時: 2006-6-12 20:44 |

Webmaster   登録日: 2004-11-7 居住地: 投稿: 3094 |

HDL記述の自由度 じっくりVHDL本を読み飛ばさずに最後まで読んでみると、薄っぺらい国内の著書とかでは紹介されていないVHDLの記述の自由度の高さを改めて知ることになる。

私は74シリーズとかはほとんど知らないし、それを使って実際に回路を組んだのは10年以上前に最初にディジタル回路設計を独学して作った286->386SXアップグレードユニットとか3state bufferを使ったその他のCPUアップグレードユニットやIDEインターフェースぐらいである。いきなり74HCxxxとか出てきても、それはいったいなんなのか調べないと分からない。 昔からのたたき上げの本職さんなら74シリーズは全部頭にたたき込まれていて、ディジタル回路はすべてそれらを組み合わせてくみ上げることができた。逆に言えば、それ以外の発想ができなくなってしまうという面もある。PLDが登場し始めてから、このあたりで古参の職人さんはPLDを毛嫌いを始める人も多かったはず。中身が見えないとかなんとか理由をつけてPLDなら少ない部品で済むところを複数の74シリーズを使って回路を組んでいたはずだ。 PLD用のデザインツールもそうした傾向をふまえて回路図入力や74シリーズに対応したライブラリーが用意されている。新参ものは74シリーズとか良く知らないし今更覚えたくないということでHDLでばりばり書くことになる。 VHDL自身も既存のデザインを利用するためにライブラリーをサポートしている。でも枯れているとは言え中身を知らない他人のデザインを使うというのはやはり気が進まないし可読性も良くない。どうせ一緒にコンパイルされて展開されるのだから自分で等価なものを書いても変わらないはず。どうしてもアルゴリズムやロジックがトリッキーで複雑なものは時間の節約のために枯れたものを使うしかないかもしれない、そういう時のためぐらい。 順序回路を組もうとする時も古典的にはラッチ(レジスタ)と組み合わせ論理(PLA)ということを連想することになるが、VHDLだとそれすら知らなくても順序回路が記述できる構文が用意されている。まさしくアルゴリズミック・ステート・マシーン(ASM)を言語レベルでサポートしているという意味で新しい。もう必要なのは入出力のタイミングチャートぐらいで、それがあればラッチをいくつ使うかとか考えなくても順序回路が記述できてしまう。 そうして書かれたHDLソースを見ると、古参な人は古い回路イメージがまったく描けなくて困惑するに違いない。フローチャートが書いてあるようなものなので、そこから最終的にコンパイルされたネットリストを想像することはもはや人間には無理かもしれない。機械というかコンパイラーならではの技である。 でもそうやると本当にこの記述で意図した通り動くのかが書いている本人も怪しくなるので、最近はいろいろな視覚化手段をデザインツールが提供している理由でもある。古参な人は展開されたネットリストを視覚的に見ることで、古典的なレジスタとPLAという構図になっていることでほっと安心するかもしれない。 |

| webadm | 投稿日時: 2006-6-24 2:39 |

Webmaster   登録日: 2004-11-7 居住地: 投稿: 3094 |

なんだか 万年時計より一回りステップアップしたものを、と考えるとスケールがちょっと大きくなりすぎるんだよね。

万年時計もそんなに小さくないロジックだけど、その少し上の規模のテーマというともうすぐ実用的なものになってしまうのがなんとも。 率直に実用的なものはおもしろくないんだよね。そういうのはキットとかであったりするし、市販のものがあったりする。すぐ何かに使いたいときは自分で作るよりキットを組み立てるか完成品を買うと思う。 んじゃ何故Byteblaster IIもどきを作ったのかというと、トランジスタ回路がおもしろかったのと誰もやってなかったから。ちゃんと確実に使えるものならレベル変換付きのバッファIC使ったものを作れば済むはなしだったし。 FETを使ったものもまだ作りたいとは思っている。でもちょっと始めるまでにはテンションが高まっていない。 DC-DCコンバーターを載せる方法も考えているけど、これもいまひとつ踏み切れない。 このスレッドはJTAGを使って汎用のディジタル、アナログ波形生成機を作ろうという発案だったけど、ハードウェアを作るのはいいけど波形エディタソフトを作るのは躊躇してしまう。そちらのほうがかなり難儀だったりする。もともと基本はソフトは作らないという姿勢だったので、それに反するということもあって頓挫。 期待していた読者には申し訳ない(といってもほとんどいないか) トラ技でもそのうち付録のCPLD基板を使った波形ジェネレータが登場するらしいのでそちらに委ねよう。 ということで勇気をもってこのプロジェクトは中止決定。 また別のものを模索しよう。 |

| スレッド表示 | 新しいものから | 前のトピック | 次のトピック | トップ |

| 投稿するにはまず登録を | |