| スレッド表示 | 新しいものから | 前のトピック | 次のトピック | 下へ |

| 投稿者 | スレッド |

|---|---|

| webadm | 投稿日時: 2006-3-18 13:43 |

Webmaster   登録日: 2004-11-7 居住地: 投稿: 3093 |

デザインのウォーミングアップから 今はFPGA/CPLD用のデザインツールも大手のは無償で使えるようになっているものの、実際にデザインを入力する段階になるとやはり設計者が頭を使わないといけない。デザインツールがやってくれるのは回路を入力した後の工程だけである。

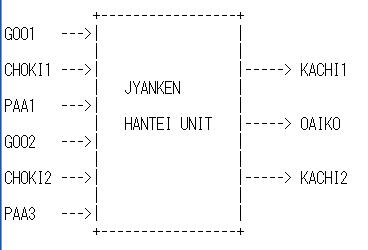

ここで論理回路設計の簡単なおさらいをしなければならない。 例としてジャンケンの判定論理装置を考えてみよう。あまり入力数が少ないと簡単に答えにたどりついてしまうので。6入力で3出力の論理ともなると古い論理回路設計の教科書に書いてある 20年ぐらい前にPCが普及してなかった頃に誰もが使っていたカルノーマップを使ってもやっかいで間違いを犯しやすい。ここはあきらめてデザインツールに最適解を出してもらうことにするのがよさそうである。それでも具体的な仕様は設計者が決めておかなければならない。 ジャンケン判定回路は対戦者2名のそれぞれの手(グー、チョキ、パーの3通り)を照合しどちらかが勝ったならそれぞれの勝利出力をONにする。おあいこの時には代わりにおあいこの信号ONにする。それ以外の不正な手が入力されたら何も出力しない。 ブロック図にすると以下の通り。  入力と出力の仕様を示すために真理値表を書いてみる。  上記の真理値表からそれぞれの出力に関する論理式を導きだすと。 KACHI1がONになるのは3つのケース(PAA1かつGOO2、GOO1かつCHOKI2、CHOKI1かつPAA2)のいずれかの場合のみであることから。 KACHI1 = (((NOT GOO1) AND (NOT CHOKI1) AND PAA1) AND (GOO2 AND (NOT CHOKI2) AND (NOT PAA2))) OR ((GOO1 AND (NOT CHOKI1) AND (NOT PAA1) AND ((NOT GOO2) AND CHOKI2 AND (NOT PAA2))) OR (((NOT GOO1) AND CHOKI1 AND (NOT PAA1)) AND ((NOT GOO2) AND (NOT CHOKI2) AND PAA2)) OAIKOがONになるのは3つのケース(GOO1かつGOO2、CHOKI1かつCHOKI2、PAA1かつPAA2)のいずれかのみであることから、 OAIKO = ((GOO1 AND (NOT CHOKI1) AND (NOT PAA1)) AND (GOO2 AND (NOT CHOKI2) AND (NOT PAA2))) OR (((NOT GOO1) AND CHOKI1 AND (NOT PAA1)) AND (NOT GOO2) AND CHOKI2 AND (NOT PAA2)) OR (((NOT GOO1) AND (NOT CHOKI1) AND PAA1) AND ((NOT GOO2) AND (NOT CHOKI2) AND PAA2)) KACHI2がONになるのは3つのケース(CHOKI1かつGOO2、PAA1かつCHOKI2、GOO1かつPAA2)のいずれかのみであることから、 KACHI2 = (((NOT GOO1) AND CHOKI1 AND (NOT PAA1)) AND (GOO2 AND (NOT CHOKI2) AND (NOT PAA2))) OR (((NOT GOO1) AND (NOT CHOKI1) AND PAA1) AND ((NOT GOO2) AND CHOKI2 AND (NOT PAA2))) OR ((GOO1 AND (NOT CHOKI1) AND (NOT PAA1)) AND ((NOT GOO2) AND (NOT CHOKI2) AND PAA2)) ここまで準備すれば、回路図入力でも論理式入力でもデザインインプットができるようになる。 次はこれらを実際にMAX+PLUSIIにインプットしてみることにする。 |

| webadm | 投稿日時: 2006-3-18 13:44 |

Webmaster   登録日: 2004-11-7 居住地: 投稿: 3093 |

回路図入力してみた結果 先の真理値表から簡易的に導き出した論理式をそのまま回路図入力して仕様である真理値表と同じ結果が得られるか確認してみた。

MAX+PLUSIIに入力したジャンケン装置の回路図 簡単に検証するために6つの入力にそれぞれクロックをベースにしてカウンター値を与えてすべての組み合わせ(64通り)についてシミュレーションしてみた。 MAX+PLUSIIによるジャンケン装置のシミュレーション結果 一応OAKIKO,KACHI1,KACHI2はそれぞれ64通りの中で3通りだけが1を出力しそれ以外は0を出力している。おのおの1を出力する際の入力条件は仕様である真理値表と一致しているのが確認できる。よく見るとヒゲが所々に出ているが、これは複数の信号が同時期に変化する際に入力信号が変化中にたまたま出力1となる条件を満たしてしまう非同期回路につきまとう現象である。 MAX+PLUSIIが入力した回路図をどのようにFPGAにマッピングしているかはreportファイル(.rpt)を見るとかかれている。良く見ると入力した回路とは似てもにつかぬものが合成されていることが確認できる。実際に論理が等価であることはシミュレーション結果を見れば一目瞭然。 MAX+PLUSIIのFPGAマッピングレポート 以下にFPGAにマッピングされた論理式を抜粋、!、&、#をそれぞれNOT,AND,ORに読み替えるば良い。 -- Node name is 'KACHI1' -- Equation name is 'KACHI1', type is output KACHI1 = _LC1_B2; -- Node name is 'KACHI2' -- Equation name is 'KACHI2', type is output KACHI2 = _LC2_B1; -- Node name is 'OAIKO' -- Equation name is 'OAIKO', type is output OAIKO = _LC1_B1; -- Node name is '~9~1' -- Equation name is '~9~1', location is LC3_B2, type is buried. -- synthesized logic cell _LC3_B2 = LCELL( _EQ001); _EQ001 = !CHOKI2 & !PAA1 & PAA2; -- Node name is ':9' -- Equation name is '_LC4_B2', type is buried _LC4_B2 = LCELL( _EQ002); _EQ002 = CHOKI1 & !GOO1 & !GOO2 & _LC3_B2; -- Node name is '~11~1' -- Equation name is '~11~1', location is LC2_B2, type is buried. -- synthesized logic cell _LC2_B2 = LCELL( _EQ003); _EQ003 = !CHOKI2 & !GOO1 & GOO2 & PAA1 # CHOKI2 & GOO1 & !GOO2 & !PAA1; -- Node name is ':11' -- Equation name is '_LC1_B2', type is buried _LC1_B2 = LCELL( _EQ004); _EQ004 = _LC4_B2 # !CHOKI1 & _LC2_B2 & !PAA2; -- Node name is '~31~1' -- Equation name is '~31~1', location is LC7_B1, type is buried. -- synthesized logic cell _LC7_B1 = LCELL( _EQ005); _EQ005 = !CHOKI2 & GOO1 & !PAA1 & PAA2 # CHOKI2 & !GOO1 & PAA1 & !PAA2; -- Node name is ':31' -- Equation name is '_LC2_B1', type is buried _LC2_B1 = LCELL( _EQ006); _EQ006 = !CHOKI1 & !GOO2 & _LC7_B1 # _LC6_B1; -- Node name is ':32' -- Equation name is '_LC6_B1', type is buried _LC6_B1 = LCELL( _EQ007); _EQ007 = CHOKI1 & !GOO1 & _LC4_B1; -- Node name is '~43~1' -- Equation name is '~43~1', location is LC5_B1, type is buried. -- synthesized logic cell _LC5_B1 = LCELL( _EQ008); _EQ008 = !CHOKI1 & !CHOKI2 & PAA1 & PAA2 # CHOKI1 & CHOKI2 & !PAA1 & !PAA2; -- Node name is ':43' -- Equation name is '_LC1_B1', type is buried _LC1_B1 = LCELL( _EQ009); _EQ009 = !GOO1 & !GOO2 & _LC5_B1 # _LC3_B1; -- Node name is '~44~1' -- Equation name is '~44~1', location is LC4_B1, type is buried. -- synthesized logic cell _LC4_B1 = LCELL( _EQ010); _EQ010 = !CHOKI2 & GOO2 & !PAA1 & !PAA2; -- Node name is ':44' -- Equation name is '_LC3_B1', type is buried _LC3_B1 = LCELL( _EQ011); _EQ011 = !CHOKI1 & GOO1 & _LC4_B1; もう人間が目で確認できるレベルでは無くなってしまっている。それはもうデザインツールのバグが無い限り不要である。 |

| webadm | 投稿日時: 2006-3-18 22:02 |

Webmaster   登録日: 2004-11-7 居住地: 投稿: 3093 |

HDLで入力してみた結果 今度はHDLでデザインをインプットしてみた。

とりあえずALTERA独自のAHDLで。今回のレベルだとPLDのコンパイラでも扱える規模なのでHDLが役不足気味ではある。まずはウォーミングアップなのでいいとしよう。回路規模が大きくなるにつれ小さなPLDではすぐ入り切らなくなりCPLDかFPGAの出番になる。その時点でもまだ回路図入力は慣れていれば手堅い方法だけど修正時の手間とかミスとかを考えるとやはりHDLが良い。 AHDLで入力したジャンケン装置のデザイン 回路図入力の時と同じ要領でシミュレーションで確認してみた。 ちょっと回路図入力の時と違って見えるのは信号の順序が違っているため。 AHDLで書いたジャンケン装置のシミュレーション結果 レポートファイルを見ても回路図入力の場合とほとんど変わりないことがわかる。合成されたロジックはまったく一緒である。なので入力の手間やメンテナンスの手間を考えるとHDLが楽なのは確か。 AHDLで書いたジャンケン装置のFPGAマッピングレポート 残念ながらどんな入力手段を使おうともソースファイルの変更管理は設計者自身でやらないといけない。今時のソフトウェア開発ツールならリビジョン管理ツールと連携して変更する前の版に戻したりとかできるが今のところデザインツールでそうしたことがサポートされているものを知らない。なのでうっかり消したり、間違ったまま保存して上書きしてしまうと、二度と元の内容は取り戻せないので細心の注意が必要である。これはなんにでも言えることだが。 |

| webadm | 投稿日時: 2006-3-18 23:11 |

Webmaster   登録日: 2004-11-7 居住地: 投稿: 3093 |

ウォーミングアップ後のもろもろの感想 ウォーミングアップをしている間にあれこれ昔の記憶とかが不思議に良くよみがえってきた。

20年前に最初に就職した会社で国産32bitスーパーマイコンを搭載したCPUボードを開発するプロジェクトが同じフロア内に発足した。私はその時ハードウェアのリードデザイナがどんな風に設計をしているのか興味があって時々そっと遠くから見ていた。当時はパソコンも初代のPC9801がある程度で、ハードウェア設計者はコンピュータの力をいっさい借りずに回路を設計していた。これは当時は当たり前のことだった。 ハードウェア設計者は見ているとほとんど机の上でメモ用紙になにか升目の入った四角形を書いてはその中に小さな長方形やら四角形をマーカーで描いては別のノートに何か設計情報を書き写していた。 後に自分でディジタル回路設計を独学した時にそれがカルノーマップというものだったということを知った。古いディジタル回路設計の教科書にはおそらくどれにでも書いてある実用的な論理回路合成方法である。直感的でありかつ手順が簡単であるため人間が行うにはとてもいい方法である。他にもクワイン・マクラスキー法といのが並んで紹介されているものもあるが、こちらは私もやってみたが人間が行うには煩雑すぎてアルゴリズムが複雑で途中で間違いをして正しい結果が得られることがなかった。おそらくコンピュータにやらせるには好都合なのかもしれない。標準LSIを使って回路を構成していた昔はカルノーマップがもっぱら用いられていたのである。 マイクロプロセッサーやPLDが一般的になると以前は標準LSIを使って組んでいたプロセッサー周辺の雑魚ロジックもPLDにひとまとめする時代になり、この段階で人間が論理圧縮する必要は無くなってしまった。PLDのコンパイラーが真理値表レベルから一気に最適なPLDの内部ロジック配線情報にマッピングしてしまうからだ。もはや誰もコンパイラーと最適化の優劣を競おうとする人はいなくなった。せいぜいロジックハザード(ヒゲやスパイク)を回避するための冗長論理を付け加える時に古いカルノーマップを持ち出す程度である。カルノーマップはロジックハザードが生じる条件を見つけるのにも大変重宝する。 30年以上前にすべて標準LSIでコンピューターレベルの回路を設計しようとしたらやはりカルノーマップに頼らざるを得なかったろう。実際そうしないと短期間に少ない部品数の回路を設計できないからだ。XeroxのPalo Alto研究所で30年前に作られたパーソナルコンピュータAltoも標準LSIと当時出たばかりのIntelのDRAMチップを使っていた。その当時既にEthernetとVGAクラスの高解像度グラフィックアダプターにマウスとキーボードを備えていたのは驚きである。30年前に今のパーソナルコンピュータの原型は既にあったのである。当時のIntelのDRAMはメモリーセルチップとセンスアンプが別チップだったのも驚きである。それほどICの集積度は当時まだ低かったということだ。その後日米がDRAM開発競争に突入してIntelは早々にDRAMから撤退して今日がある。 今ならAltoもFPGAにすっぽり入ってしまうのかもしれない。マイクロプログラミング方式のCISCアーキテクチャだからちょっとそのままでは難しいかもしれない。でも回路規模は写真を見る限りではずいぶん小さい感じがする。ALUだけで基板一枚使っているし。 夢としては仮想記憶をサポートしたCPUをFPGAを使ってつくれたらいいなと思う。たぶんやっている人は少ないはず。Sun Microsystemも最初は仮想記憶をサポートしないMC68000を二つ使ってむりやりデマンドページングとかを実現していた。その後例外発生後に命令を再実行可能なように仕様変更されたMC68010が出てCPUは一つで済むようになった。MMUとかもCPUに内蔵されるまではカスタムで外付けされていたはず。今からするとしょぼいものだった。でも4.2BSDベースのSunOSは瞬く間に仮想記憶をサポートしたUNIXを世間に知らしめるものとなった。元祖のAT&TのUNIXはまだサポートしてなかったからね。あわててSystem VのR3で仮想記憶をやっとサポートした。その前のR2はVAX版も仮想記憶サポート無しなのは知る人ぞ知るところ。 やはりメモリが数MBも使えてswappingも仮想記憶も無いと今時はつらいものがある。20年前に飛ぶように売れたDECのVAX/VMSは512KBのメインメモリで複数ユーザーで利用できた。もっともVAXは1ページが512バイトとディスクのセクターサイズと同一で粒度が細かかったからそれが可能だったのかも。カーネルはすべてアセンブラでかかれていたのでノンページド部は100KBしかメモリを占有しなかった。残りはすべてページブルなので参照されたときにページングされる。 AppleのMachintoshもはじめは仮想記憶などなくて少ないメインメモリでGUIアプリケーションが動作するというのが注目をあつめた。次第に大きなアプリケーションが開発されるようになって、そうしたアプリケーションを使うにはメモリを山ほど増設しなければならず次々と大きなメモリが搭載できる上位機種に買い換えが必要だった。ある時点でついに仮想記憶をサポートして複数の巨大なアプリケーションを同時に使うことが可能になった。 WindowsもNTになってやっと仮想記憶を使うようになった。それ以前の32bitアプリケーションはMACと一緒で無理矢理メモリにロードして動かしていたようなものだった。 組み込み用でもメモリがリニアーにしか管理できないCPUだと複数のアプリケーションを入れ替わり立ち替わり走らせる用途にはちょっとつらいものがある。仮想記憶といわなくてもページ単位やセグメント単位でメモリを細かい粒度で管理できるとうれしい。 DECの爆発的に売れたミニコンピューターPDP-11も初期のIntel x86がまねたようなセグメント方式のメモリ管理をサポートしていた。それによってマルチタスク・マルチユーザーなシステムにとても重宝した。現在の組み込み用マイコンはメモリコントローラとかを内蔵しているので自分でメモリ管理ユニットを外付けしようとしても無理なんだよね。DRAMとの間につけても仕方ないし。CPUの仮想アドレスとメモリコントローラの間に入れないといけないからねMMUは。 やはり自分で作るしかないのかも。 話を元に戻すと、ハードウェア設計の世界ではコンピューターの力を最大限に活用してもう人間が論理圧縮とかしなくても良く、もっと大きな規模でシステムを考えるのに注力できるようになったのはいいことだ。 ソフトウェア設計者はさすがにすべてアセンブラでかく必要はなくなったといえ、細かいところに足をすくわれて泥まみれな状態から抜け出せていない気がする。もっとコンピュータを信じて活用しないといけないと思う。 |

| スレッド表示 | 新しいものから | 前のトピック | 次のトピック | トップ |

| 投稿するにはまず登録を | |